# Nano Scale Disruptive Silicon-Plasmonic Platform for Chipto-Chip Interconnection

# **Dual Die Communication Module functional specification**

Deliverable no.: D5.1

Due date: 04/30/2012

Actual Submission date: 04/30/2012

Authors: ST

Work package(s): WP5

Distribution level: CO<sup>1</sup> (NAVOLCHI Consortium)

Nature: Document, available online in the restricted area

of the NAVOLCHI webpage

### List of Partners concerned

| Partner<br>number | Partner name                                                  | Partner<br>short | Country     | Date<br>enter | Date exit |

|-------------------|---------------------------------------------------------------|------------------|-------------|---------------|-----------|

|                   |                                                               | name             |             | project       | project   |

| 1                 | Karlsruher Institut für Technologie                           | KIT              | Germany     | M1            | M36       |

| 2                 | INTERUNIVERSITAIR MICRO-<br>ELECTRONICA CENTRUM VZW           | IMCV             | Belgium     | M1            | M36       |

| 3                 | TECHNISCHE UNIVERSITEIT<br>EINDHOVEN                          | TU/e             | Netherlands | M1            | M36       |

| 4                 | RESEARCH AND EDUCATION LABORATORY IN INFORMATION TECHNOLOGIES | AIT              | Greece      | M1            | M36       |

| 5                 | UNIVERSITAT DE VALENCIA                                       | UVEG             | Spain       | M1            | M36       |

| 6                 | STMICROELECTRONICS SRL                                        | ST               | Italy       | M1            | M36       |

| 7                 | UNIVERSITEIT GENT                                             | UGent            | Belgium     | M1            | M36       |

**PP** = Restricted to other programme participants (including the Commission Services)

**RE** = Restricted to a group specified by the consortium (including the Commission Services)

**CO** = Confidential, only for members of the consortium (including the Commission Services)

$<sup>\</sup>mathbf{PU} = \mathbf{Public}$

**Deliverable Report**Last update 01/31/2012

Version 1

#### Deliverable Responsible

Organization: STMicroelectronics Contact Person: Alberto Scandurra

Address: Stradale Primosole, 50 – 95121 Catania

Italy

Phone: +39 095 740 4432 Fax: +39 095 740 4008 E mail: alberto scandurra@s

E-mail: alberto.scandurra@st.com

#### **Executive Summary**

This document describes the Dual Die Communication Module (DDCM) architecture and functionality. The DDCM is an Intellectual Property (IP) allowing two dice within a System in Package (SiP) to communicate to each other. Its functionality covers all the layers foreseen by the protocol stack, from transport to data link, but the physical layer (PHY), that can be of different nature, i.e. electrical or optical. This document addresses a first DDCM implementation supporting electrical PHY; in a subsequent phase of the project the DDCM will be modified so to support an optical PHY based on plasmonics.

### Change Records

| Version        | Date       | Changes | Author            |

|----------------|------------|---------|-------------------|

| 0.1 (draft)    | 2012-04-19 | Start   | Alberto Scandurra |

| 1 (submission) | 2012-04-30 |         | Alberto Scandurra |

# **Contents**

| 1 I | NTRODUCTIO    | N                            | 5  |

|-----|---------------|------------------------------|----|

|     |               |                              |    |

| 2 P | PARAMETERS    |                              | 7  |

|     | Top level     | 7                            |    |

|     | Initiators    | 7                            |    |

|     | Targets       | 8                            |    |

|     | Virtual wire  |                              |    |

|     |               | ins synchronization          | g  |

|     | Retiming      | 9                            |    |

|     | FIFOs         | 10                           |    |

|     | Credit-based  | I flow control               | 10 |

| 3 I | NTERFACES     |                              | 12 |

|     | System        | 12                           |    |

|     | Test          | 12                           |    |

|     | Configuration |                              |    |

|     | _             | 13                           |    |

|     | Target        | 14                           |    |

|     | Virtual wire  | s 16                         |    |

|     | Programmin    | g 16                         |    |

|     | Security end  | oder                         | 17 |

|     | Physical cha  | nnel                         | 17 |

|     |               | roller PHY adapter interface | 18 |

|     | Timing        | 18                           |    |

| 4 R | REGISTERS     |                              | 20 |

|     | Registers ac  | cess path                    | 37 |

|     |               |                              |    |

| 5 A | ARCHITECTUI   | RE                           | 40 |

| 6 B | BUILDING-BLO  | OCKS                         | 43 |

|     | Transmitter   |                              |    |

|     |               | 45<br>annel                  | 13 |

|     |               | hannel                       |    |

|     |               | ut Channel                   |    |

# **FP7-ICT-2011-7** Project-No. 288869 NAVOLCHI – D5.1

### **Deliverable Report** Last update 01/31/2012 Version 1

| Error! Bookmark not define  Error! Bookmark not define  Error! Bookmark not define |

|------------------------------------------------------------------------------------|

| Error! Bookmark not define<br>Error! Bookmark not define                           |

| Error! Bookmark not define<br>Error! Bookmark not define                           |

| Error! Bookmark not define<br>Error! Bookmark not define                           |

| Error! Bookmark not define                                                         |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

| ••••••                                                                             |

|                                                                                    |

### 1 Introduction

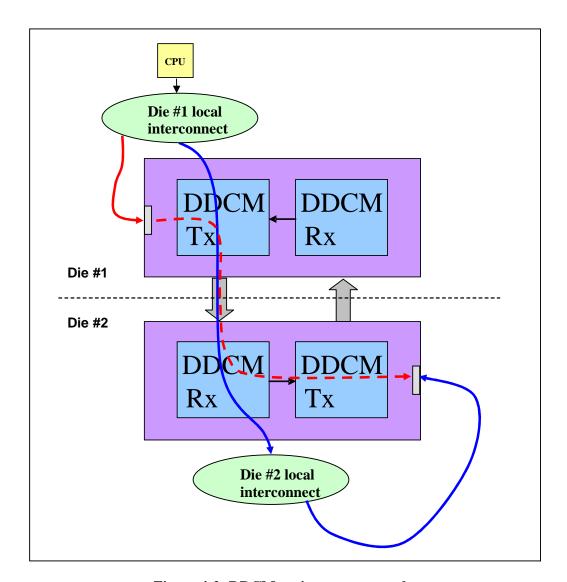

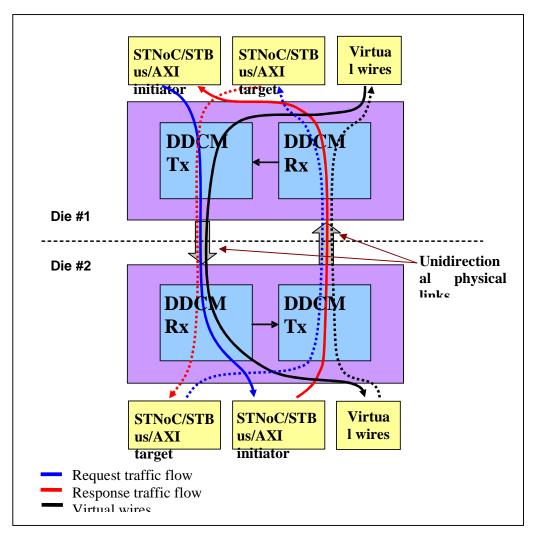

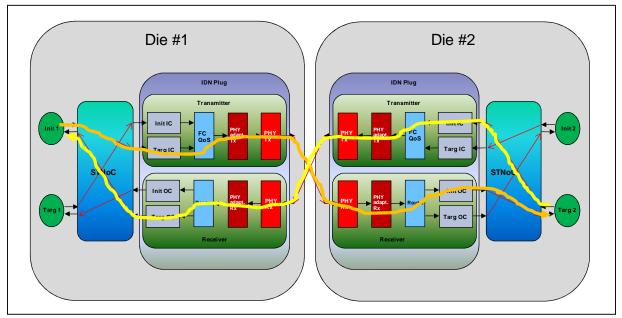

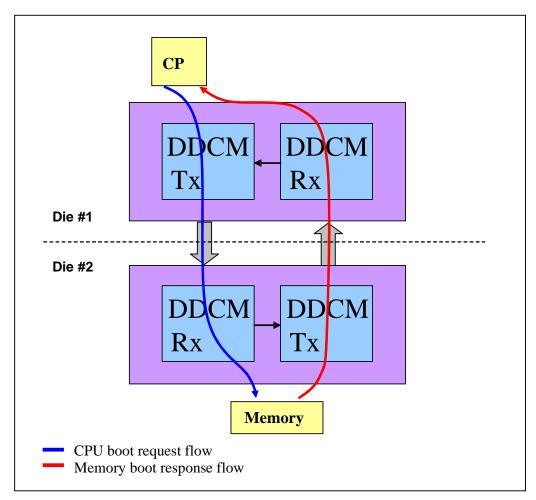

The **Dual Die Communication Module** (abbreviated **DDCM**) is the building-block responsible for the interconnection of different dice within a so called Network in Package (NiP), the communication system enabling inter dice data transmission in the context of Systems in Package (SiP) technology.

From an architectural point of view it represents the evolution of the STAC (STNoC Advanced off-chip Communication module).

The main features of the DDCM, differing from STAC, are:

- support of **Spidergon STNoC** initiator and target interfaces;

- IP flit size and frequency conversion

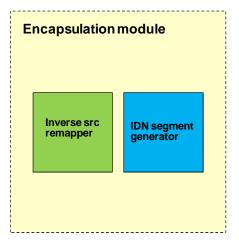

- integrated **src-remapper**;

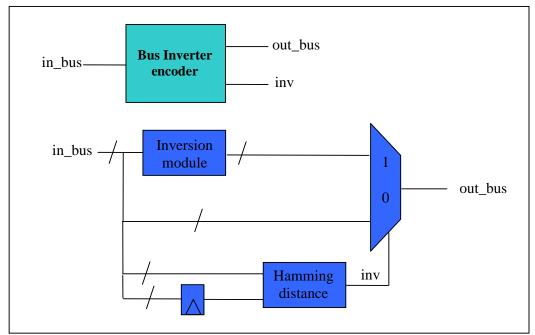

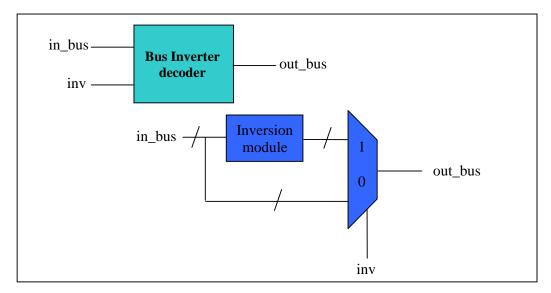

- integrated encoder/decoder for **dynamic power saving**;

- registers and logic for on-chip debugging and performance metrics calculation.

The differences between DDCM and STAC are summarized in the following table.

| Feature                          | <b>DDCM</b> | STAC    |

|----------------------------------|-------------|---------|

| Initiator/target interface       | STNoC       | VSTNoC  |

| Initiator/target interface size  | Any         | 72 bits |

| Flit size conversion             | Yes         | No      |

| Frequency conversion             | Yes         | No      |

| Src remapper                     | Yes         | No      |

| Dynamic power saving             | Yes         | No      |

| On-chip debugging and monitoring | Yes         | No      |

Table 0.1 – Differences between DDCM and STAC

In the future the DDCM will support the following additional features:

- support of **STBus** initiator and target interfaces;

- support of AMBA-AXI initiator and target interfaces;

- integrated encryption/decryption module for **transactions security**;

- support of bidirectional communication with two neighbourhood dice.

The differences between future DDCM and STAC are summarized in the following table.

| Feature                      | DDCM                   | STAC     |

|------------------------------|------------------------|----------|

| Initiator/target interface   | STNoC, STBus, AMBA-AXI | VSTNoC   |

| External dice interfaces     | 2                      | 1        |

| Encryption/decryption module | Internal               | External |

Table 0.2 – Differences between future DDCM and STAC

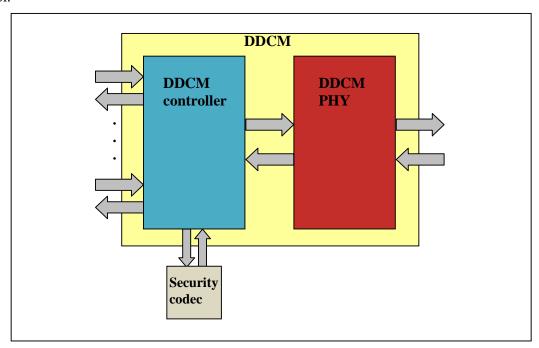

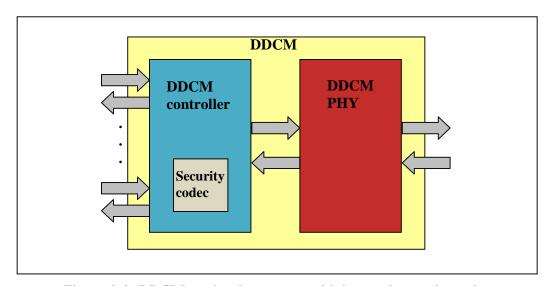

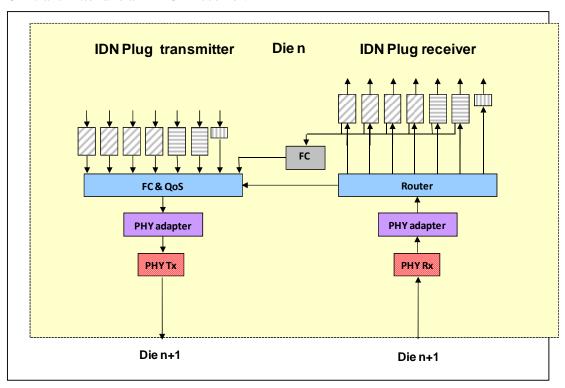

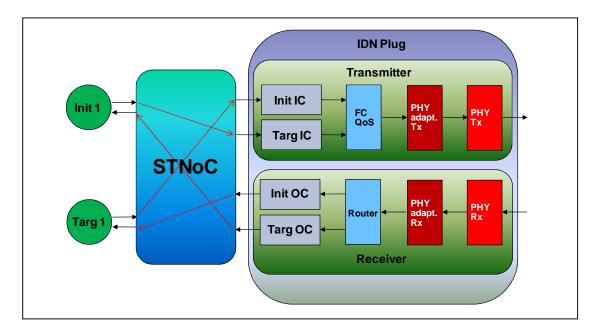

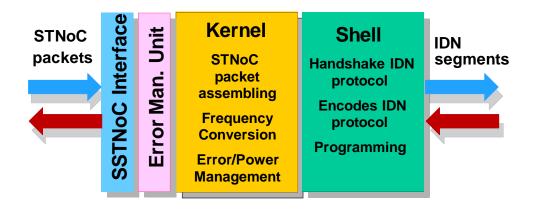

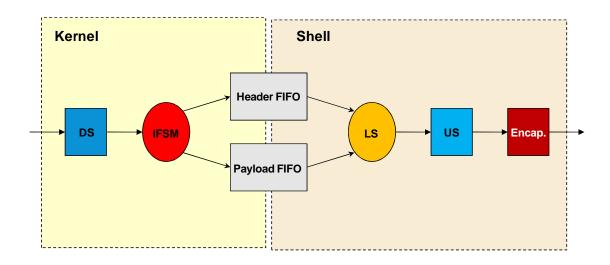

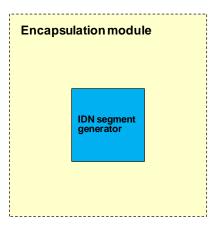

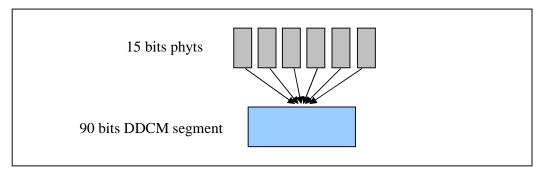

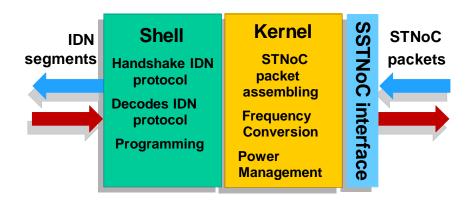

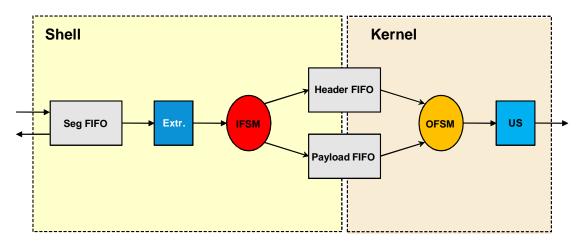

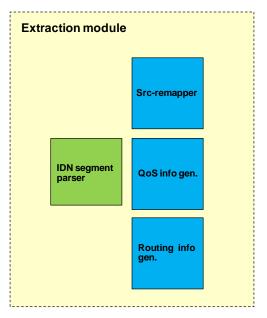

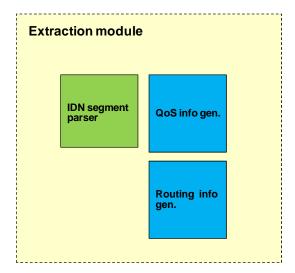

According to a widely used approach, the DDCM is considered composed of two main building blocks:

the DDCM controller, responsible for managing incoming/outgoing STNoC traffic and IDN segments, generating them through STNoC flits encapsulation and preparing them to be sent to the PHY transmitter, as well as collecting them from the PHY receiver; • the DDCM PHY, responsible for transmitting output phyts across the physical link and collecting inputs phyts from the physical link.

The next two figures show the DDCM structure in terms of top level building-blocks. Figure 1.1 shows the current structure with external security encoder/decoder, while figure 1.2 shows the future structure with the security encoder/decoder embedded within the DDCM top level.

Figure 0-1: DDCM top level structure with external security codec

Figure 0-2: DDCM top level structure with internal security codec

## 2 Parameters

The DDCM is a parametric design that, depending on the SoC where it is used, can be configured properly in order to meet system requirements and needs in terms of interfaces, FIFOs sizes, clock domains synchronization and functionality.

The tables in next subsections list and describe the the DDCM parameters.

# Top level

| Name             | Description                                                     | Range      | Default |

|------------------|-----------------------------------------------------------------|------------|---------|

| init_port_nb     | Number of STNoC initiators.                                     | 0 to 16    | 4       |

| targ_port_nb     | Number of STNoC targets.                                        | 0 to 16    | 4       |

| virtual_wires_on | Specifies if to support virtual wires.                          | true/false | true    |

| src_remapper_on  | Specifies if to instantiate the src remapper                    | true/false | false   |

| power_saving_on  | Specifies if to instantiate the codec for dynamic power saving. | true/false | false   |

**Table 2.1: Top level parameters**

### **Initiators**

| Name                           | Description                                                              | Range                     | Default |

|--------------------------------|--------------------------------------------------------------------------|---------------------------|---------|

| init_i_ds_vn1_on               | Specifies if the downstream interface is present in virtual network #1.  | true/false                | true    |

| init_i_ds_vn2_on               | Specifies if the downstream interface is present in virtual network #2.  | true/false                | false   |

| init_i_ds_flit_size            | Downstream interface flit size.                                          | 16,18,32,36,64,72,128,144 | 72      |

| init_i_ds_flit_extra_bits_size | Downstream interface extra bits number.                                  | 0 to 144                  | 0       |

| init_i_ds_flit_id_atomic_on    | Specifies if the flit_id_atomic port is present in downstream interface. | true/false                | false   |

| init_i_ds_flit_id_3_on         | Specifies if the flid_id_3 port is present in downstream interface.      | true/false                | false   |

| init_i_ds_flit_id_err_on       | Specifies if the flid_id_err port is present in downstream interface.    | true/false                | false   |

| init_i_ds_four_be_on           | Specifies if the four_be port is present in downstream interface.        | true/false                | false   |

| init_i_ds_four_be_size         | Downstream interface four_be port size.                                  | 0 to 4                    | 0       |

| init_i_us_vn1_on               | Specifies if the upstream interface is present in virtual network #1.    | true/false                | true    |

| init_i_us_vn2_on               | Specifies if the upstream interface is present in virtual network #2.    | true/false                | false   |

| init_i_us_flit_size            | Upstream interface flit size.                                            | 16,18,32,36,64,72,128,144 | 72      |

| init_i_us_flit_extra_bits_size | Upstream interface extra bits number.                               | 0 to 144   | 0     |

|--------------------------------|---------------------------------------------------------------------|------------|-------|

| init_i_us_flit_id_3_on         | Specifies if the flid_id_3 port is present in upstream interface.   | true/false | false |

| init_i_us_flit_id_err_on       | Specifies if the flid_id_err port is present in upstream interface. | true/false | false |

| init_i_us_four_be_on           | Specifies if the four_be port is present in upstream interface.     | true/false | false |

| init_i_us_four_be_size         | Upstream interface four_be port size.                               | 0 to 4     | 0     |

**Table 2.2: Initiators parameters**

# **Targets**

| Name                           | Description                                                              | Range                     | Default |

|--------------------------------|--------------------------------------------------------------------------|---------------------------|---------|

| targ_i_ds_vn1_on               | Specifies if the downstream interface is present in virtual network #1.  | true/false                | true    |

| targ_i_ds_vn2_on               | Specifies if the downstream interface is present in virtual network #2.  | true/false                | false   |

| targ_i_ds_flit_size            | Downstream interface flit size.                                          | 16,18,32,36,64,72,128,144 | 72      |

| targ_i_ds_flit_extra_bits_size | Downstream interface extra bits number.                                  | 0 to 144                  | 0       |

| targ_i_ds_flit_id_atomic_on    | Specifies if the flit_id_atomic port is present in downstream interface. | true/false                | false   |

| targ_i_ds_flit_id_3_on         | Specifies if the flid_id_3 port is present in downstream interface.      | true/false                | false   |

| targ_i_ds_flit_id_err_on       | Specifies if the flid_id_err port is present in downstream interface.    | true/false                | false   |

| targ_i_ds_four_be_on           | Specifies if the four_be port is present in downstream interface.        | true/false                | false   |

| targ_i_ds_four_be_size         | Downstream interface four_be port size.                                  | 0 to 4                    | 0       |

| targ_i_us_vn1_on               | Specifies if the upstream interface is present in virtual network #1.    | true/false                | true    |

| targ_i_us_vn2_on               | Specifies if the upstream interface is present in virtual network #2.    | true/false                | false   |

| targ_i_us_flit_size            | Upstream interface flit size.                                            | 16,18,32,36,64,72,128,144 | 72      |

| targ_i_us_flit_extra_bits_size | Upstream interface extra bits number.                                    | 0 to 144                  | 0       |

| targ_i_us_flit_id_3_on         | Specifies if the flid_id_3 port is present in upstream interface.        | true/false                | false   |

| targ_i_us_flit_id_err_on       | Specifies if the flid_id_err port is present in upstream interface.      | true/false                | false   |

| targ_i_us_four_be_on           | Specifies if the four_be port is present in upstream interface.          | true/false                | false   |

| targ_i_us_four_be_size         | Upstream interface four_be port size.                                    | 0 to 4                    | 0       |

**Table 2.3: Targets parameters**

### Virtual wires

| Name              | Description                                                                        | Range   | Default |

|-------------------|------------------------------------------------------------------------------------|---------|---------|

| bundle_i_tx_size  | Size, in terms of number of wires, of virtual wires bundle #i in DDCM transmitter. | 0 to 80 | 80      |

| bundle_i_sam_rate | Sampling rate of the bundle #i of the virtual wires DDCM transmitter port.         | 0 to 10 | 1       |

| bundle_i_rx_size  | Size, in terms of number of wires, of virtual wires bundle #i in DDCM receiver.    | 0 to 80 | 80      |

**Table 2.4: Virtual wires parameters**

# Clock domains synchronization

| Name                  | Description                                                                | Range  | Default |

|-----------------------|----------------------------------------------------------------------------|--------|---------|

| idn_plug_synch_dff_nb | Number of synchronization flip-flops in DDCM clock domain.                 | 1 to 8 | 2       |

| prog_synch_dff_nb     | Number of synchronization flip-flops in programming clock domain.          | 1 to 8 | 2       |

| phy_tx_synch_dff_nb   | Number of synchronization flip-flops in DDCM PHY transmitter clock domain. | 1 to 8 | 2       |

| phy_rx_synch_dff_nb   | Number of synchronization flip-flops in DDCM PHY receiver clock domain.    | 1 to 8 | 2       |

Table 2.5: Clock domains synchronization parameters

# Retiming

| Name                | Description                                                                                    | Range      | Default |

|---------------------|------------------------------------------------------------------------------------------------|------------|---------|

| init_i_ds_retiming  | Specifies whether a retiming stage has to be istantiated at initiator #i downstream interface. | true/false | false   |

| targ_i_ds_retiming  | Specifies whether a retiming stage has to be istantiated at target #i downstream interface.    | true/false | false   |

| init _i_us_retiming | Specifies whether a retiming stage has to be istantiated at initiator #i upstream interface.   | true/false | false   |

| targ_i_us_retiming  | Specifies whether a retiming stage has to be istantiated at target #i upstream interface.      | true/false | false   |

**Table 2.6: Retiming parameters**

### **FIFOs**

| Name                     | Description                                                                                                                          | Range    | Default |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------|---------|

| init_i_tx_fifo_size      | Size of the FIFO related to initiator port #i in DDCM transmitter.                                                                   | 2 to 128 | 8       |

| targ_i_tx_fifo_size      | Size of the FIFO related to target port #i in DDCM transmitter.                                                                      | 2 to 128 | 8       |

| init_i_rx_fifo_ size     | Size of IDN segment FIFO related to initiator port #i in DDCM receiver.                                                              | 8 to 128 | 8       |

| targ_i_rx_fifo_ size     | Size of IDN segment FIFO related to target port #i in DDCM receiver.                                                                 | 8 to 128 | 8       |

| targ_i_rx_fifo_saf_reset | Value after reset of the register specifying if store & forward mechanism has to be applied by the different FIFOs in DDCM receiver. | 0 to 1   | 1       |

**Table 2.7: FIFOs parameters**

# Credit-based flow control

| Name                         | Description                                                                                                 | Range                       | Default |

|------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------|---------|

| targ_i_rx_fifo_ threshold    | targ_i_rx_fifo_ threshold Number of freed locations the IDN segment FIFO                                    |                             | 3       |

|                              | associated to target port #i of DDCM receiver must have in order to send a credit information.              | n: 2 <sup>n</sup> locations |         |

|                              | have in order to send a credit information.                                                                 | ( 0<= n <= 5)               |         |

|                              |                                                                                                             | 6 : half FIFO               |         |

|                              |                                                                                                             | 7 : whole FIFO              |         |

| init_i_rx_fifo_ threshold    | Number of freed locations the IDN segment FIFO #i                                                           | 0 to 7                      | 3       |

|                              | associated to an initiator port of DDCM receiver must have in order to send a credit information.           | n: 2 <sup>n</sup> locations |         |

|                              |                                                                                                             | ( 0<= n <= 5)               |         |

|                              |                                                                                                             | 6 : half FIFO               |         |

|                              |                                                                                                             | 7 : whole FIFO              |         |

| targ_i_rx_fifo_credit_period | Value after reset of the frequency with which the                                                           | 0 to 7                      | 7       |

|                              | credits information has to be sent for target IDN segment FIFO #i from the QoS module of the DDCM receiver. | 0:4 cycles                  |         |

|                              |                                                                                                             | 1:8 cycles                  |         |

|                              |                                                                                                             | 2:16 cycles                 |         |

|                              |                                                                                                             | 3 : 32 cycles               |         |

|                              |                                                                                                             | 4 : 64 cycles               |         |

|                              |                                                                                                             | 5:128 cycles                |         |

|                              |                                                                                                             | 6:256 cycles                |         |

|                              |                                                                                                             | 7:512 cycles                |         |

| init_i_rx_fifo_credit_period |                                                                                                             |                             | 7       |

|                              | credits information has to be sent for initiator IDN segment FIFO #i from the QoS module of the DDCM        | 0:4 cycles                  |         |

|                              | receiver.                                                                                                   | 1:8 cycles                  |         |

| FP7-ICT-2011-7     |

|--------------------|

| Project-No. 288869 |

| NAVOLCHI – D5.1    |

### **Deliverable Report** Last update 01/31/2012 Version 1

|  | 2 . 16 avalas  |

|--|----------------|

|  | 2 : 16 cycles  |

|  | 3 : 32 cycles  |

|  | 4 : 64 cycles  |

|  | 5 : 128 cycles |

|  | 6:256          |

|  | 7:512          |

**Table 2.8: Credit-based flow control parameters**

### 3 Interfaces

### **System**

The system interface consists of the clocks on which the operation of the DDCM is based, and the asynchronous reset used for the initialization of the block.

Notice that the reset signal is managed as an asynchronous signal, and its synchronization with respect to the related clock is performed by proper modules inside the DDCM.

| Signal name | I/O | Timing | Description                   |

|-------------|-----|--------|-------------------------------|

| rst_n       | I   | N/A    | Asynchronous active low reset |

| clk_plug    | I   | N/A    | DDCM clock                    |

| clk_prog    | I   | N/A    | Programming clock             |

| clk_phy_tx  | I   | N/A    | DDCM PHY transmitter clock    |

| clk_phy_rx  | I   | N/A    | DDCM PHY receiver clock       |

Table 3.1 –System interface

### **Test**

The test interface consists of a set of ports allowing to test the DDCM digital modules (scan test) and the physical channel and its controller (PHY) after manufacturing.

Besides the usual scan test signals, i.e. tst\_scanenable, tst\_scanin, tst\_scanout, a tst\_mode port is required in order to bypass synchronizers and any synchronization logic during test, because of the need of a unique reset and a unique clock.

| Signal name     | I/O | Timing | Description                       |

|-----------------|-----|--------|-----------------------------------|

| tst_scanenable  | I   | N/A    | Scan test enable                  |

| tst_scanin      | I   | N/A    | Scan test input                   |

| tst_scanout     | О   | N/A    | Scan test output                  |

| tst_mode        | I   | N/A    | Test mode enable                  |

| tst_phy_sce_sel | I   | N/A    | PHY test source selector          |

| tst_pg_hi<15:0> | I   | N/A    | Pattern generator high data input |

| tst_pg_lo<15:0> | I   | N/A    | Pattern generator low data input  |

| tst_pg_vld      | I   | N/A    | Pattern generator data valid      |

**Table 3.2 – Test interface**

Notice that the width of scan test input and output signals will depend on the number of scan chains created within the DDCM, according to synthesis results.

### **Configuration**

The configuration interface consists of a set of inputs (mode pins) allowing to configure the DDCM functionality after reset, so to be adapted to different contexts. Notice that the same functionality can be re-programmed through the correspondent registers accessible via the DDCM programming interface.

It's important to point out that this set of configuration signals is related to the DDCM implementation working with the electrical PHY able to operate in both DCE/SCE modes. Using a different PHY and related PHY adapter these parameters realistically will change. The configuration interface is synchronous with the clk\_plug clock.

| Signal name   | I/O | Timing | Description                                        |  |  |

|---------------|-----|--------|----------------------------------------------------|--|--|

| phy_tx_width  | I   | Late   | When '0' all the 16 bits of the PHY transmitter    |  |  |

|               |     |        | interface are used, when '1' only 8 are used       |  |  |

| phy_rx_width  | I   | Late   | When '0' all the 16 bits of the PHY receiver       |  |  |

|               |     |        | interface are used, when '1' only 8 are used       |  |  |

| phy_mode      | I   | Late   | When '0' the PHY works in DCE mode, when '1'       |  |  |

|               |     |        | in SCE mode                                        |  |  |

| lpe_tx_bypass | I   | Late   | When '0' the bus inverter transmitter for dynamic  |  |  |

|               |     |        | power optimization is bypassed, when '1' it's used |  |  |

**Table 3.3 – Configuration interface**

### **Initiator**

The initiator interface consists of standard STNoC initiator ports, i.e. a set of signals replicated a number of times according to how many initiators are connected to the DDCM.

If an initiator interface is synchronous with a clock differing from the DDCM main clock, the required frequency conversion is performed inside the DDCM itself.

The following tables report the downstream and upstream interfaces for a generic STNoC initiator, identified as initiator #i ( $1 \le i \le 16$ ).

| Signal name                                                                                                                                                                   | I/O | Timing | Description |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|-------------|

| init_i_ds_flit <init_i_ds_flit_size+init_i_ds_flit_extra_bits_size-< td=""><td>I</td><td>Early</td><td>STNoC flit</td></init_i_ds_flit_size+init_i_ds_flit_extra_bits_size-<> | I   | Early  | STNoC flit  |

| 1:0>                                                                                                                                                                          |     |        |             |

| init_i_ds_flit_id<1:0>                                                                                                                                                        | I   | Early  | Flit        |

|                                                                                                                                                                               |     |        | identifier  |

| init_i_ds_flit_id_3                                                                                                                                                           | I   | Early  | Flit        |

|                                                                                                                                                                               |     |        | identifier  |

|                                                                                                                                                                               |     |        | bit 3       |

| init_i_ds_flit_id_err<1:0>                                                                                                                                                    | I   | Early  | Error       |

|                                                                                                                                                                               |     |        | marker      |

| init_i_ds_flit_id_atomic                                                                                                                                                      | I   | Early  | Atomic      |

|                                                                                                                                                                               |     |        | transaction |

|                                                                                                                                                                               |     |        | flag        |

| init_i_ds_four_be <init_i_ds_four_be_size-1:0></init_i_ds_four_be_size-1:0>                                                                                                   | I   | Early  | Four byte-  |

|                                                                                                                                                                               |     |        | enables     |

| init_i_ds_vn1_val                                                                                                                                                             | I   | Early  | Virtual     |

|                                                                                                                                                                               |     |        | network #1  |

|                                                                                                                                                                               |     |        | valid       |

| init_i_ds_vn1_credit                                                                                                                                                          | O   | Early  | Virtual     |

|                                                                                                                                                                               |     |        | network #1  |

|                                                                                                                                                                               |     |        | credit      |

| init_i_ds_vn2_val                                                                                                                                                             | I   | Early  | Virtual     |

|                                                                                                                                                                               |     |        | network #2  |

|                      |   |       | valid      |

|----------------------|---|-------|------------|

| init_i_ds_vn2_credit | O | Early | Virtual    |

|                      |   |       | network #2 |

|                      |   |       | credit     |

Table 3.4 – STNoC initiator downstream interface

| Signal name                                                                                                                                                                   | I/O | Timing | Description     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|-----------------|

| init_i_us_flit <init_i_us_flit_size+init_i_us_flit_extra_bits_size-< td=""><td>O</td><td>Early</td><td>STNoC flit</td></init_i_us_flit_size+init_i_us_flit_extra_bits_size-<> | O   | Early  | STNoC flit      |

| 1:0>                                                                                                                                                                          |     |        |                 |

| init_i_us_flit_id<1:0>                                                                                                                                                        | O   | Early  | Flit identifier |

| init_i_us_flit_id_3                                                                                                                                                           | O   | Early  | Flit identifier |

|                                                                                                                                                                               |     |        | bit 3           |

| init_i_us_flit_id_err<1:0>                                                                                                                                                    | O   | Early  | Error marker    |

| init_i_us_flit_id_atomic                                                                                                                                                      | O   | Early  | Atomic          |

|                                                                                                                                                                               |     |        | transaction     |

|                                                                                                                                                                               |     |        | flag            |

| init_i_us_four_be <init_i_us_four_be_size-1:0></init_i_us_four_be_size-1:0>                                                                                                   | O   | Early  | Four byte-      |

|                                                                                                                                                                               |     |        | enables         |

| init_i_us_vn1_val                                                                                                                                                             | O   | Early  | Virtual         |

|                                                                                                                                                                               |     |        | network #1      |

|                                                                                                                                                                               |     |        | valid           |

| init_i_us_vn1_credit                                                                                                                                                          | I   | Early  | Virtual         |

|                                                                                                                                                                               |     |        | network #1      |

|                                                                                                                                                                               |     |        | credit          |

| init_i_us_vn2_val                                                                                                                                                             | O   | Early  | Virtual         |

|                                                                                                                                                                               |     |        | network #2      |

|                                                                                                                                                                               |     |        | valid           |

| init_i_us_vn2_credit                                                                                                                                                          | I   | Early  | Virtual         |

|                                                                                                                                                                               |     |        | network #2      |

|                                                                                                                                                                               |     |        | credit          |

**Table 3.5 – STNoC initiator upstream interface**

### **Target**

The target interface consists of standard STNoC target ports, i.e. a set of signals replicated a number of times according to how many targets are connected to the DDCM.

If a target interface is synchronous with a clock differing from the DDCM main clock, the required frequency conversion is performed inside the DDCM itself.

The following tables report the downstream and upstream interfaces for a generic STNoC target, identified as target #i ( $1 \le i \le 16$ ).

| Signal name                                                                                                                                                                   | I/O | Timing | Description |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|-------------|

| targ_i_ds_flit <targ_i_ds_flit_size+targ_i_ds_flit_extra_bits_size-< td=""><td>I</td><td>Early</td><td>STNoC flit</td></targ_i_ds_flit_size+targ_i_ds_flit_extra_bits_size-<> | I   | Early  | STNoC flit  |

| 1:0>                                                                                                                                                                          |     |        |             |

| targ_i_ds_flit_id<1:0>                                                                                                                                                        | I   | Early  | Flit        |

|                                                                                                                                                                               |     |        | identifier  |

| targ_i_ds_flit_id_3                                                         | I | Early | Flit identifier bit 3           |

|-----------------------------------------------------------------------------|---|-------|---------------------------------|

| targ_i_ds_flit_id_err<1:0>                                                  | I | Early | Error<br>marker                 |

| targ_i_ds_flit_id_atomic                                                    | I | Early | Atomic transaction flag         |

| targ_i_ds_four_be <targ_i_ds_four_be_size-1:0></targ_i_ds_four_be_size-1:0> | I | Early | Four byte-<br>enables           |

| targ_i_ds_vn1_val                                                           | I | Early | Virtual<br>network #1<br>valid  |

| targ_i_ds_vn1_credit                                                        | О | Early | Virtual<br>network #1<br>credit |

| targ_i_ds_vn2_val                                                           | I | Early | Virtual<br>network #2<br>valid  |

| targ_i_ds_vn2_credit                                                        | О | Early | Virtual<br>network #2<br>credit |

Table 3.6 –STNoC target downstream interface

| Signal name                                                                                                                             | I/O | Timing | Description                     |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----|--------|---------------------------------|

| targ_i_us_flit <targ_i_us_flit_size+targ_i_us_flit_extra_bits_size-<br>1:0&gt;</targ_i_us_flit_size+targ_i_us_flit_extra_bits_size-<br> | О   | Early  | STNoC flit                      |

| targ_i_us_flit_id<1:0>                                                                                                                  | О   | Early  | Flit identifier                 |

| targ_i_us_flit_id_3                                                                                                                     | 0   | Early  | Flit identifier bit 3           |

| targ_i_us_flit_id_err<1:0>                                                                                                              | О   | Early  | Error<br>marker                 |

| targ_i_us_flit_id_atomic                                                                                                                | О   | Early  | Atomic transaction flag         |

| targ_i_us_four_be <targ_i_us_four_be_size-1:0></targ_i_us_four_be_size-1:0>                                                             | О   | Early  | Four byte-<br>enables           |

| targ_i_us_vn1_val                                                                                                                       | О   | Early  | Virtual<br>network #1<br>valid  |

| targ_i_us_vn1_credit                                                                                                                    | I   | Early  | Virtual<br>network #1<br>credit |

| targ_i_us_vn2_val                                                                                                                       | O   | Early  | Virtual                         |

|                      |   |       | network<br>valid             | #2 |

|----------------------|---|-------|------------------------------|----|

| targ_i_us_vn2_credit | I | Early | Virtual<br>network<br>credit | #2 |

Table 3.7 –STNoC target upstream interface

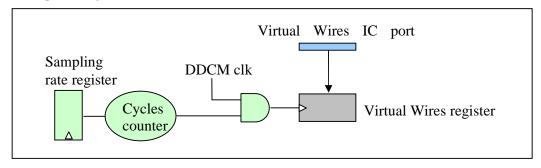

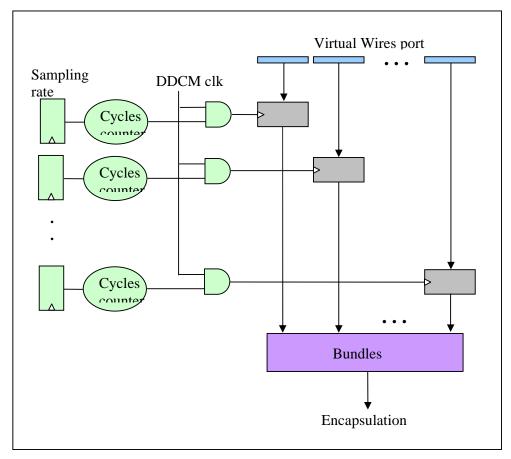

#### Virtual wires

The virtual routing interface consists of a set of bundles configurable in terms of size, whose individual bits represent specific signals carrying specific information, such as interrupts, power down control, asynchronous events. Such bundles are sampled at given rates, and depending on them their content is transmitted across the DDCM to the second die.

| Signal name                        | I/O | Timing | Description                   |

|------------------------------------|-----|--------|-------------------------------|

| bundle_1_tx< bundle_1_tx_size-1:0> | I   | N/A    | Virtual wires input bundle #1 |

| bundle_2_tx< bundle_2_tx_size-1:0> | I   | N/A    | Virtual wires input bundle #2 |

| bundle_3_tx< bundle_3_tx_size-1:0> | I   | N/A    | Virtual wires input bundle #3 |

| bundle_4_tx< bundle_4_tx_size-1:0> | I   | N/A    | Virtual wires input bundle #4 |

| bundle_5_tx< bundle_5_tx_size-1:0> | I   | N/A    | Virtual wires input bundle #5 |

Table 3.8 –DDCM transmitter virtual wires interface

| Signal name                        | I/O | Timing | Description                    |

|------------------------------------|-----|--------|--------------------------------|

| bundle_1_rx< bundle_1_rx_size-1:0> | О   | Early  | Virtual wires output bundle #1 |

| bundle_2_rx< bundle_2_rx_size-1:0> | О   | Early  | Virtual wires output bundle #2 |

| bundle_3_rx< bundle_3_rx_size-1:0> | О   | Early  | Virtual wires output bundle #3 |

| bundle_4_rx< bundle_4_rx_size-1:0> | O   | Early  | Virtual wires output bundle #4 |

| bundle_5_rx< bundle_5_rx_size-1:0> | O   | Early  | Virtual wires output bundle #5 |

Table 3.9 –DDCM receiver virtual wires interface

Notice that virtual wires inputs are asynchronous, and they are synchronized internally to the DDCM.

### **Programming**

The programming interface consists of a standard STBus type 1 interface allowing to access the internal registers in order to configure the operation of the DDCM, mainly in terms of QoS policy. The configuration of the DDCM registers can be done either during the initialization phase or on-fly, in the sense that the registers specifying the QoS policy can be modified even during the normal operation of the block.

The programming interface is synchronous with the clk\_prog clock.

| Signal name | I/O | Timing | Description   |

|-------------|-----|--------|---------------|

| prog_req    | I   | Late   | Request       |

| prog_eop    | I   | Late   | End of packet |

| prog_opc<3:0>     | I | Late  | Operation code   |

|-------------------|---|-------|------------------|

| prog_add<7:2>     | I | Late  | Address          |

| prog_data<31:0>   | I | Late  | Write data       |

| prog_be<3:0>      | I | Late  | Byteenables      |

| prog_r_req        | О | Early | Response request |

| prog_r_opc        | O | Early | Operation status |

| prog_r_data<31:0> | О | Early | Read data        |

**Table 3.10 – Programming interface**

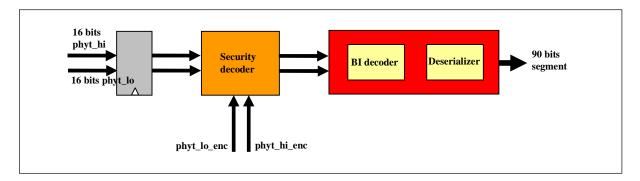

### Security encoder

The security encoder interface consists of a set of inputs representing the masks to be used for the encoding/decoding of the outgoing/incoming flits from/to the DDCM PHY adapter, in order to encrypt them for protection against any hacking.

| Signal name          | I/O | Timing | Description              |

|----------------------|-----|--------|--------------------------|

| phyt_hi_enc_tx<15:0> | I   | N/A    | Transmitter phyt_hi mask |

| phyt_lo_enc_tx<15:0> | I   | N/A    | Transmitter phyt_lo mask |

| phyt_hi_enc_rx<15:0> | I   | N/A    | Receiver phyt_hi mask    |

| phyt_lo_enc_rx<15:0> | I   | N/A    | Receiver phyt_lo mask    |

**Table 3.11 – Security encoder interface**

### Physical channel

The physical channel interface (PHY) is responsible for the actual transmission of data between dice

According to the layered approach followed by DDCM implementation, the PHY can change case by case according to specific system requirements and technology availability. The PHY interface will then change accordingly.

This section reports the interface of the PHY in case of 16 bits wide electrical physical channel following the DCE/SCE approach. Differently PHY structure realistically will have different interfaces.

For any detail refer to the specific PHY documentation.

When a data is ready to be transmitted a data valid signal is issued; moreover, the clock is required to be transmitted as well, since the DDCM transmitter and receiver are physically located in two different chips and then are clocked by different clocks, so that the communication between them is asynchronous.

DDCM transmitter PHY is synchronous with the clk tx clock.

| Signal name   | I/O | Timing | Description                            |

|---------------|-----|--------|----------------------------------------|

| tx_phyt<15:0> | O   | late   | Data to be transmitted                 |

| tx_valid      | О   | late   | Data valid signal                      |

| tx_clock      | O   | late   | Transmission clock for synchronization |

Table 3.12 – Physical channel transmitter interface

DDCM receiver PHY is instead synchronous with the clk\_rx clock.

| Signal name   | I/O | Timing | Description                            |

|---------------|-----|--------|----------------------------------------|

| rx_phyt<15:0> | I   | late   | Data to be transmitted                 |

| rx_valid      | I   | late   | Data valid signal                      |

| rx_clock      | I   | late   | Transmission clock for synchronization |

Table 3.13 – Physical channel receiver interface

### DDCM controller PHY adapter interface

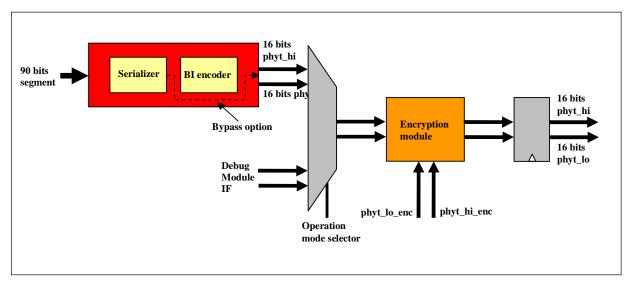

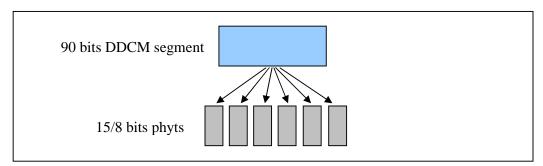

Since, thanks to the layered protocol approach, the DDCM can be implemented with different PHY structures (DCE, SCE, parallel, serial, optical, RF), it's convenient to specify also the PHY adapter interface, even if it is internal to the DDCM.

The interfaces described in the following tables are related to an electrical PHY working in DCE/SCE mode. In case of different PHY, the PHY adapter interfaces with the DDCM digital parts will not change, while the interfaces with the PHY will change according to the specific PHY structure.

| Signal name          | I/O | Timing | Description                                   |

|----------------------|-----|--------|-----------------------------------------------|

| seg<89:0>            | I   | Early  | DDCM segment coming from layer B              |

| seg_val              | I   | Early  | DDCM segment valid flag (active high)         |

| seg_ack              | O   | Early  | DDCM segment acknowledge (active high)        |

| tx_phy_mode          | О   | Early  | PHY operation mode (DCE/SCE) control          |

|                      |     |        | flag                                          |

| tx_phyt_hi<15:0>     | O   | Early  | Phyt to be sent during clock rising edge      |

| tx_phyt_lo<15:0>     | O   | Early  | Phyt to be sent during clock falling edge     |

| tx_phyt_valid        | О   | Early  | Specifies the phyt is ready to be transmitted |

| tx_phy_tx_clk_enable | О   | Early  | PHY transmitter clock enable (active high)    |

Table 3.14 – PHY adapter transmitter interface

Notice that, if the phy\_mode configuration input is set to '1', and then the PHY works in SCE mode, only phyt\_hi output is meaningful for the PHY adapter transmitter, and only phyt\_hi input is meaningful for the PHY adapter receiver.

| Signal name      | I/O | Timing | Description                                        |

|------------------|-----|--------|----------------------------------------------------|

| rx_phyt_hi<15:0> | I   | Early  | Phyt received by the PHYduring clock rising edge   |

| rx_phyt_lo<15:0> | I   | Early  | Phyt received by the PHY during clock falling edge |

| rx_phyt_valid    | I   | Early  | Specifies the phyt is ready to be kept             |

| seg<89:0>        | О   | Early  | DDCM segment going to layer B                      |

| seg_val          | О   | Early  | DDCM segment valid flag (active high)              |

Table 3.15 – PHY adapter receiver interface

### Timing

The timing of all the DDCM ports depends on the technology used to synthesize the design; as example, the timing to be adopted when using the CMOS technology at 28 nm is defined as follows:

**FP7-ICT-2011-7** Project-No. 288869 NAVOLCHI – D5.1

**Deliverable Report** Last update 01/31/2012 Version 1

- **Early** means within the 30% of the clock cycle; an early input refers to a signal coming from a register located into a module very close to the DDCM; an early output refers to a signal leaving a register of the DDCM.

- Late means within the 60% of the clock cycle; a late input refers to a signal coming from a module placed quite far from the DDCM, so that the delay of the wire crossed by such a signal has an impact on the arrival time to the DDCM input; a late output refers to a signal crossing some combinational logic before leaving the DDCM.

- **Mid** means within the 40% of the clock cycle; a mid input refers to a signal coming from a module placed not far from the DDCM, so that the delay of the wire crossed by such a signal has not a big impact on the arrival time to the DDCM input; a mid output refers to a signal crossing some small combinational logic before leaving the DDCM.

- N/A means an input is asynchronous with respect to DDCM clock period.

# **4 Registers**

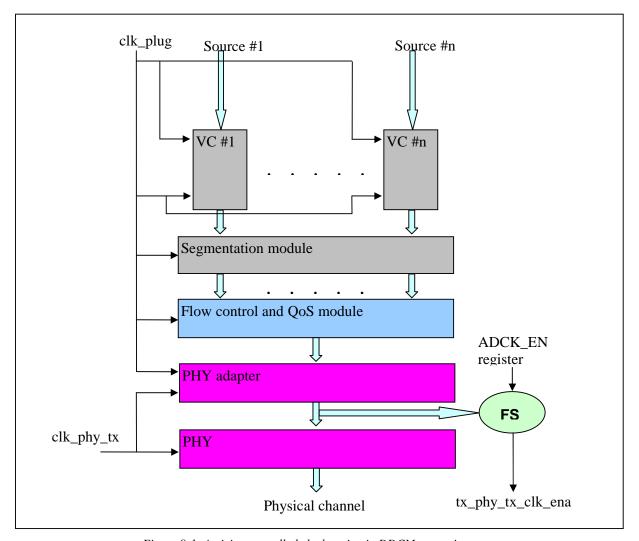

The DDCM is programmable in terms of some functionalities, in particular layer A (PHY adapter, PHY) operation and routing (virtual channels), trough a set of registers. QoS management is also planned to be configurable via registers.

DDCM registers are memory-mapped, and all of them are 32-bits wide and 32 bits-aligned.

The list of registers contained within the optional configuration module of the DDCM is shown in next table in case of a DDCM with N virtual channels.

| Address   | Name                              | Description                            |

|-----------|-----------------------------------|----------------------------------------|

| Base+0x00 | PHY_WIDTH                         | PHY width actually used for            |

|           |                                   | transmission                           |

| Base+0x04 | PHY_MODE                          | PHY transmission mode (DCE, SCE)       |

| Base+0x08 | INIT_1_8_TX_VC_ID                 | Tx virtual channel – initiator port    |

|           |                                   | association (set 1)                    |

| Base+0x0C | INIT_9_16_TX_VC_ID                | Tx virtual channel – initiator port    |

|           |                                   | association (set 2)                    |

| Base+0x10 | TARG_1_8_TX_VC_ID                 | Tx virtual channel – target port       |

|           |                                   | association (set 1)                    |

| Base+0x14 | TARG_9_16_TX_VC_ID                | Tx virtual channel – target port       |

|           |                                   | association (set 2)                    |

| Base+0x18 | INIT_1_8_RX_FIFO_ID               | Rx FIFO – initiator port association   |

|           |                                   | (set 1)                                |

| Base+0x1C | INIT_9_16_RX_FIFO_ID <sup>2</sup> | Rx FIFO – initiator port association   |

|           |                                   | (set 2)                                |

| Base+0x20 | TARG_1_8_RX_FIFO_THRESHOLD        | Target rx FIFOs threshold for credits  |

|           |                                   | transmission (set 1)                   |

| Base+0x24 | TARG_9_16_RX_FIFO_THRESHOLD       | Target rx FIFOs threshold for credits  |

|           |                                   | transmission (set 2)                   |

| Base+0x28 | INIT_1_8_RX_FIFO_THRESHOLD        | Initiator rx FIFOs threshold for       |

|           |                                   | credits transmission (set 1)           |

| Base+0x2C | INIT_9_16_RX_FIFO_THRESHOLD       | Initiator rx FIFOs threshold for       |

|           |                                   | credits transmission (set 2)           |

| Base+0x30 | TARG_1_8_CREDIT_TIMEOUT           | Target rx FIFOs credit transmission    |

|           |                                   | timeout (set 1)                        |

| Base+0x34 | TARG_9_16_CREDIT_TIMEOUT          | Target rx FIFOs credit transmission    |

|           |                                   | timeout (set 2)                        |

| Base+0x38 | INIT_1_8_CREDIT_TIMEOUT           | Initiator rx FIFOs credit transmission |

|           |                                   | timeout (set 1)                        |

| Base+0x3C | INIT_9_16_CREDIT_TIMEOUT          | Initiator rx FIFOs credit transmission |

|           |                                   | timeout (set 2)                        |

| Base+0x40 | TARG_1_8_RX_FIFO_PRI              | Target FIFO priorities in DDCM rx      |

|           |                                   | for FC arbiter (set 1)                 |

| Base+0x44 | TARG_9_16_RX_FIFO_PRI             | Target FIFO priorities in DDCM rx      |

<sup>2</sup> Registers specifying ports to FIFOs association are not supported by DDCM v1.0

|           |                       | for FC arbiter (set 2)                  |

|-----------|-----------------------|-----------------------------------------|

| Base+0x48 | INIT_1_8_RX_FIFO_PRI  | Initiator FIFO priorities in DDCM rx    |

|           |                       | for FC arbiter (set 1)                  |

| Base+0x4C | INIT_9_16_RX_FIFO_PRI | Initiator FIFO priorities in DDCM rx    |

|           |                       | for FC arbiter (set 2)                  |

| Base+0x50 | QOS                   | Enables specific QoS algorithms         |

| Base+0x54 | BUNDLE_SIZE           | Virtual wires bundles size              |

| Base+0x58 | ADCK_EN               | Activity driven clock enable for each   |

|           |                       | clock domain                            |

| Base+0x5C | BI_TX_BYPASS          | BI transmitter bypass enable            |

| Base+0x60 | TARG_RX_FIFO_SAF      | Target FIFO store and forward enable    |

| Base+0x64 | WIRES_SAM_RATE        | Virtual wires sampling rate             |

| Base+0x68 | DDCM_PHY_FREQ_RATIO   | Info on frequency ratio between         |

|           |                       | DDCM and DDCM PHY                       |

| Base+0x6C | IPORT_1_BWL           | Bandwidth limiter parameters for        |

|           |                       | initiator port #1                       |

| Base+0x70 | IPORT_2_BWL           | Bandwidth limiter parameters for        |

|           |                       | initiator port #2                       |

|           |                       |                                         |

| Base+0xA4 | IPORT_15_BWL          | Bandwidth limiter parameters for        |

|           |                       | initiator port #15                      |

| Base+0xA8 | IPORT_16_BWL          | Bandwidth limiter parameters for        |

|           |                       | initiator port #16                      |

| Base+0xAC | PHY_DEBUG_MODE        | PHY input selector in debug mode        |

| Base+0xB0 | INIT_1_8_TX_VC_PRI    | Initiator tx virtual channel priorities |

|           |                       | (set 1)                                 |

| Base+0xB4 | INIT_9_16_TX_VC_PRI   | Initiator tx virtual channel priorities |

|           |                       | (set 2)                                 |

| Base+0xB8 | TARG_1_8_TX_VC_PRI    | Target tx virtual channel priorities    |

|           |                       | (set 1)                                 |

| Base+0xBC | TARG_9_16_TX_VC_PRI   | Target tx virtual channel priorities    |

|           |                       | (set 2)                                 |

**Table 4-1 – DDCM registers**

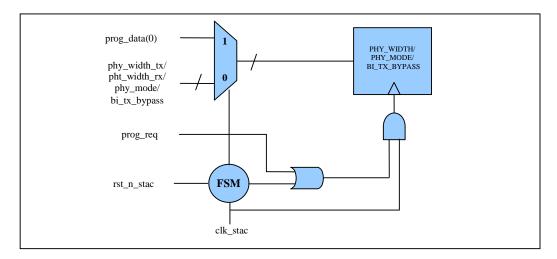

The PHY\_WIDTH, PHY\_MODE, and BI\_TX\_BYPASS registers are set after reset through the DDCM input ports having the same names; such ports are sampled after reset and their values are loaded into the correspondent DDCM registers; subsequently they can be re-programmed dynamically through the DDCM programming interface. This is shown in figure 4.1.

Figure 4-1 – DDCM programming logic

The following tables show in detail the structure and the meaning of each register. Notice that "not used" means that FFs are not physically present, while "reserved" means the FFs are present but their meaning is not defined at the moment. In both cases, write operations have no effect while read operations return '0'.

| Name      | Address   | Bits                                                    | Description                                                 |

|-----------|-----------|---------------------------------------------------------|-------------------------------------------------------------|

| PHY_WIDTH | Base+0x00 | <0>                                                     | Specify the DDCM transmitter PHY interface data (phyt) size |

|           |           |                                                         | 0 : 16 bits                                                 |

|           |           |                                                         | 1 : 8 bits                                                  |

|           |           | <1> Specify the DDCM receiver PHY interface (phyt) size |                                                             |

|           |           |                                                         | 0 : 16 bits                                                 |

|           |           |                                                         | 1 : 8 bits                                                  |

|           |           | <31:2>                                                  | Not used                                                    |

Table 4-2 – PHY\_WIDTH register structure

| Name     | Address   | Bits                               | Description                 |  |

|----------|-----------|------------------------------------|-----------------------------|--|

| PHY_MODE | Base+0x04 | <0> Specify the PHY operation mode |                             |  |

|          |           |                                    | 0 : Dual Clock Edge (DCE)   |  |

|          |           |                                    | 1 : Single Clock Edge (SCE) |  |

|          |           | <31:1>                             | Not used                    |  |

**Table 4-3 – PHY\_MODE register structure**

| Name              | Address   | Bits    | Bits Description                                        |  |

|-------------------|-----------|---------|---------------------------------------------------------|--|

| INIT_1_8_TX_VC_ID | Base+0x08 | <3:0>   | Specify the ID of the VC connected to initiator port #1 |  |

|                   |           | <7:4>   | Specify the ID of the VC connected to initiator port #2 |  |

|                   |           |         |                                                         |  |

|                   |           | <31:28> | Specify the ID of the VC connected to initiator port #8 |  |

Table 4-4-INIT\_1\_8\_TX\_VC\_ID register structure

| Name               | Address   | Bits    | Description                                              |

|--------------------|-----------|---------|----------------------------------------------------------|

| INIT_9_16_TX_VC_ID | Base+0x0C | <3:0>   | Specify the ID of the VC connected to initiator port #9  |

|                    |           | <7:4>   | Specify the ID of the VC connected to initiator port #10 |

|                    |           |         |                                                          |

|                    |           | <31:28> | Specify the ID of the VC connected to initiator port #16 |

Table 4-5- INIT\_9\_16\_TX\_VC\_ID register structure

| Name              | Address   | Bits    | Description                                          |

|-------------------|-----------|---------|------------------------------------------------------|

| TARG_1_8_TX_VC_ID | Base+0x10 | <3:0>   | Specify the ID of the VC connected to target port #1 |

|                   |           | <7:4>   | Specify the ID of the VC connected to target port #2 |

|                   |           |         |                                                      |

|                   |           | <31:28> | Specify the ID of the VC connected to target port #8 |

Table 4-6-TARG\_1\_8\_TX\_VC\_ID register structure

| Name               | Address   | Bits    | Description                                           |

|--------------------|-----------|---------|-------------------------------------------------------|

| TARG_9_16_TX_VC_ID | Base+0x14 | <3:0>   | Specify the ID of the VC connected to target port #9  |

|                    |           | <7:4>   | Specify the ID of the VC connected to target port #10 |

|                    |           |         |                                                       |

|                    |           | <31:28> | Specify the ID of the VC connected to target port #16 |

Table 4-7- TARG\_9\_16\_TX\_VC\_ID register structure

| Name                | Address   | Bits  | Description                                               |

|---------------------|-----------|-------|-----------------------------------------------------------|

| INIT_1_8_RX_FIFO_ID | Base+0x18 | <3:0> | Specify the ID of the FIFO connected to initiator port #1 |

|                     |           | <7:4> | Specify the ID of the FIFO connected to initiator port    |

|      | #2                                                        |

|------|-----------------------------------------------------------|

|      |                                                           |

|      | 111                                                       |

| <31: | Specify the ID of the FIFO connected to initiator port #8 |

Table 4-8-INIT\_1\_8\_RX\_FIFO\_ID register structure

| Name                           | Address | Bits    | Description                                                |

|--------------------------------|---------|---------|------------------------------------------------------------|

| INIT_9_16_RX_FIFO_ID Base+0x1C |         | <3:0>   | Specify the ID of the FIFO connected to initiator port #9  |

|                                |         | <7:4>   | Specify the ID of the FIFO connected to initiator port #10 |

|                                |         |         |                                                            |

|                                |         | <31:28> | Specify the ID of the FIFO connected to initiator port #16 |

Table 4-9- INIT\_9\_16\_RX\_FIFO\_ID register structure

| Name                           | Address   | Bits    | Description                                                                        |

|--------------------------------|-----------|---------|------------------------------------------------------------------------------------|

| TARG_1_8_RX_FIFO_THRESHOL<br>D | Base+0x20 | <2:0>   | Threshold for credit information transmission from target FIFO #1 in DDCM receiver |

|                                |           |         | 0 : 1 cell                                                                         |

|                                |           |         | n : 2 <sup>n</sup> cells (0 < n < 5)                                               |

|                                |           |         | 6 : half FIFO                                                                      |

|                                |           |         | 7 : whole FIFO                                                                     |

|                                |           | <5:3>   | Threshold for credit information transmission from target FIFO #2 in DDCM receiver |

|                                |           | <8:6>   | Threshold for credit information transmission from target FIFO #3 in DDCM receiver |

|                                |           | <11:9>  | Threshold for credit information transmission from target FIFO #4 in DDCM receiver |

|                                |           | <14:12> | Threshold for credit information transmission from target FIFO #5 in DDCM receiver |

|                                |           | <17:15> | Threshold for credit information transmission from target FIFO #6 in DDCM receiver |

|                                |           | <20:18> | Threshold for credit information transmission from target FIFO #7 in DDCM receiver |

| <23:21> | Threshold for credit information transmission from target FIFO #8 in DDCM receiver |

|---------|------------------------------------------------------------------------------------|

| <31:24> | Not used                                                                           |

Table 4-10– TARG\_1\_8\_RX\_FIFO\_THRESHOLD register structure

| Name                            | Address   | Bits    | Description                                                                         |

|---------------------------------|-----------|---------|-------------------------------------------------------------------------------------|

| TARG_2_16_RX_FIFO_THRESHOL<br>D | Base+0x24 | <2:0>   | Threshold for credit information transmission from target FIFO #9 in DDCM receiver  |

|                                 |           |         | 0 : 1 cell                                                                          |

|                                 |           |         | n : 2 <sup>n</sup> cells (0 < n < 5)                                                |

|                                 |           |         | 6 : half FIFO                                                                       |

|                                 |           |         | 7 : whole FIFO                                                                      |

|                                 |           | <5:3>   | Threshold for credit information transmission from target FIFO #10 in DDCM receiver |

|                                 |           | <8:6>   | Threshold for credit information transmission from target FIFO #11 in DDCM receiver |

|                                 |           | <11:9>  | Threshold for credit information transmission from target FIFO #12 in DDCM receiver |

|                                 |           | <14:12> | Threshold for credit information transmission from target FIFO #13 in DDCM receiver |

|                                 |           | <17:15> | Threshold for credit information transmission from target FIFO #14 in DDCM receiver |

|                                 |           | <20:18> | Threshold for credit information transmission from target FIFO #15 in DDCM receiver |

|                                 |           | <23:21> | Threshold for credit information transmission from target FIFO #16 in DDCM receiver |

|                                 |           | <31:24> | Not used                                                                            |

Table 4-11- TARG\_9\_16\_RX\_FIFO\_THRESHOLD register structure

| Name                       | Address   | Bits  | Description                                                                           |

|----------------------------|-----------|-------|---------------------------------------------------------------------------------------|

| INIT_1_8_RX_FIFO_THRESHOLD | Base+0x28 | <2:0> | Threshold for credit information transmission from initiator FIFO #1 in DDCM receiver |

|                            |           |       | 0:1 cell                                                                              |

| 1 |         |                                                      |

|---|---------|------------------------------------------------------|

|   |         | n : 2 <sup>n</sup> cells (0 < n < 5)                 |

|   |         | 6 : half FIFO                                        |

|   |         | 7 : whole FIFO                                       |

|   | <5:3>   | Threshold for credit information                     |

|   |         | transmission from initiator FIFO #2 in DDCM receiver |

|   | <0.0>   | Threshold for credit information                     |

|   |         | transmission from initiator FIFO #3                  |

|   |         | in DDCM receiver                                     |

|   | <11.9>  | Threshold for credit information                     |

|   |         | transmission from initiator FIFO #4 in DDCM receiver |

|   |         |                                                      |

|   | <14:12> | Threshold for credit information                     |

|   |         | transmission from initiator FIFO #5 in DDCM receiver |

|   | <17:15> | Threshold for credit information                     |

|   |         | transmission from initiator FIFO #6                  |

|   |         | in DDCM receiver                                     |

|   | <20.10> | Threshold for credit information                     |

|   |         | transmission from initiator FIFO #7 in DDCM receiver |

|   | <23.21> | Threshold for credit information                     |

|   |         | transmission from initiator FIFO #8                  |

|   |         | in DDCM receiver                                     |

|   | <31:24> | Not used                                             |

Table 4-12\_INIT\_1\_8\_RX\_FIFO\_THRESHOLD register structure

| Name                        | Address   | Bits   | Description                                                                            |

|-----------------------------|-----------|--------|----------------------------------------------------------------------------------------|

| INIT_9_16_RX_FIFO_THRESHOLD | Base+0x2C | <2:0>  | Threshold for credit information transmission from initiator FIFO #9 in DDCM receiver  |

|                             |           |        | 0 : 1 cell                                                                             |

|                             |           |        | n : 2 <sup>n</sup> cells (0 < n < 5)                                                   |

|                             |           |        | 6 : half FIFO                                                                          |