## Nano Scale Disruptive Silicon-Plasmonic Platform for Chipto-Chip Interconnection

# Electroluminescence from QD stack embedded within conductive oxides (>1µW)

| Milestone no.:          | MS21                                              |

|-------------------------|---------------------------------------------------|

| Due date:               | 31 April 2013                                     |

| Actual Submission date: | 20 May 2013                                       |

| Authors:                | imec                                              |

| Work package(s):        |                                                   |

| Distribution level:     | RE <sup>1</sup> (NAVOLCHI Consortium)             |

| Nature:                 | document, available online in the restricted area |

|                         | of the NAVOLCHI webpage                           |

#### List of Partners concerned

| Partner | Partner name                                                        | Partner | Country     | Date    | Date    |

|---------|---------------------------------------------------------------------|---------|-------------|---------|---------|

| number  |                                                                     | short   |             | enter   | exit    |

|         |                                                                     | name    |             | project | project |

| 1       | Karlsruher Institut für Technologie                                 | KIT     | Germany     | M1      | M36     |

| 2       | INTERUNIVERSITAIR MICRO-<br>ELECTRONICA CENTRUM VZW                 | IMEC    | Belgium     | M1      | M36     |

| 3       | TECHNISCHE UNIVERSITEIT<br>EINDHOVEN                                | TU/e    | Netherlands | M1      | M36     |

| 4       | RESEARCH AND EDUCATION<br>LABORATORY IN INFORMATION<br>TECHNOLOGIES | AIT     | Greece      | M1      | M36     |

| 5       | UNIVERSITAT DE VALENCIA                                             | UVEG    | Spain       | M1      | M36     |

| 6       | STMICROELECTRONICS SRL                                              | ST      | Italy       | M1      | M36     |

| 7       | UNIVERSITEIT GENT                                                   | UGent   | Belgium     | M1      | M36     |

$<sup>\</sup>mathbf{PU} = \mathbf{Public}$

1

**PP** = Restricted to other programme participants (including the Commission Services)

**RE** = Restricted to a group specified by the consortium (including the Commission Services)

**CO** = Confidential, only for members of the consortium (including the Commission Services)

#### **FP7-ICT-2011-7** Project-No. 288869 NAVOLCHI – MS21

#### Deliverable Responsible

| Organization:   | imec                        |

|-----------------|-----------------------------|

| Contact Person: | Dries Van Thourhout         |

| Address:        | St. Pietersnieuwstraat 41   |

|                 | 9000 Gent                   |

|                 | Belgium                     |

| Phone:          | +32 9 2643438               |

| E-mail:         | dries.vanthourhout@ugent.be |

|                 |                             |

#### **Executive Summary**

This document reports on reaching the milestone of demonstration of stacks incorporating colloidal quantum dots exhibiting electro-luminescnce and being compatible with future integration in waveguide devices.

#### Change Records

| Version        | Date       | Changes | Author              |

|----------------|------------|---------|---------------------|

| 0.1 (draft)    | 2013-05-15 | Start   | Dries Van Thourhout |

| 1 (submission) |            |         | Dries Van Thourhout |

### **Contents**

| 1. | INTRODUCTION | 1 |

|----|--------------|---|

|    |              |   |

| 2. | FUTURE WORK  | 5 |

# 1. Introduction

The goal of this milestone was to demonstrate a structure which can emit up to 1 microwatt in the near-infrared using colloidal nanocrystals as light emitters. Moreover, this structure should be integrated on the silicon photonics platform. We propose to use the device architecture used by Wood et al. where colloidal nanocrystals are sandwiched between two insulating layers (e.g. aluminum oxide or silicon nitride) and contacted with metal anode and cathode contacts.

Compared to direct – current injection schemes (e.g. REF), the advantages are:

- Processing robust (no air sensitivity, controlled deposition techniques) and compatible with nanocrystals.

- Easy integration on silicon photonics circuits, both passive waveguides and resonators.

- Intriniscally pulsed operation and no Ohmic heating.

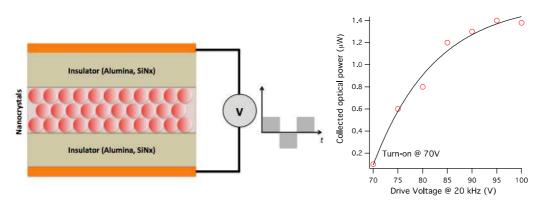

# Figure 1: Bulk device layout (left) and collected power as a function of drive voltage using a 20 kHz block wave (right).

Bulk devices were fabricated using 1 mm x 1 mm – electrodes. The insulating layers of aluminum oxide was deposited using atomic layer deposition at  $125^{\circ}$ C to yield atomically flat layers of the oxide with well controlled thickness of 50 nm. The nanocrystal layer was deposited using spincoating from an apolar solvent to yield approximately 50 nm thick layers (i.e. 6-7 monolayers) of PbS/CdS core/shell nanoparticles emitting at 1550 nm. The core/shell structure provides additional long term stability, even under electrical excitation.

The optical power was collected with a high NA fibre and sent to a power meter to detect up to 60 microwatt/cm<sup>2</sup> using a 20 kHz/70 Vppp block wave. We believe this can be further improved by increasing the voltage drop over the nanocyrstal layer itself:

- tuning the layer thickness of the nanocrystals

- thinning the insulator layers without causing breakdown

- using higher k oxides (e.g. Hafnium oxide)

Also the electrical drive parameters can be optimized by going to higher drive frequencies (now possible with new AC source) and voltages. New waveforms (besides block waves) should also be investigated.

# 2. Future work

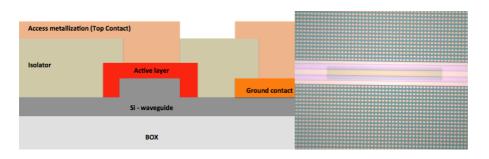

Future work will focus on integrating this structure on SOI waveguides. A mask was designed and fabricated at IMEC for this purpose (see also M31).

A generic cross section is provided in figure 2. The 'active layer' will be similar to the bulk device stack depicted in figure 1 (left). The processing steps are compatible with standard UV lithograpy and lift-off techniques as is shown in a figure 2 (right) where a first attempt at patterning the aluminum oxide layer using lift-off on a silicon rib waveguide is shown.

Figure 2: (left) Schematic of cross section of integrated device and (right) first attempt at alumina patterning on standard SOI waveguides.