Department of Information Technology and Electrical Engineering

# NAVOLCHI WP6 Integration, Characterization & Testing

Claudia Hoessbacher, Juerg Leuthold

Institute of Electromagnetic Fields (IFH)

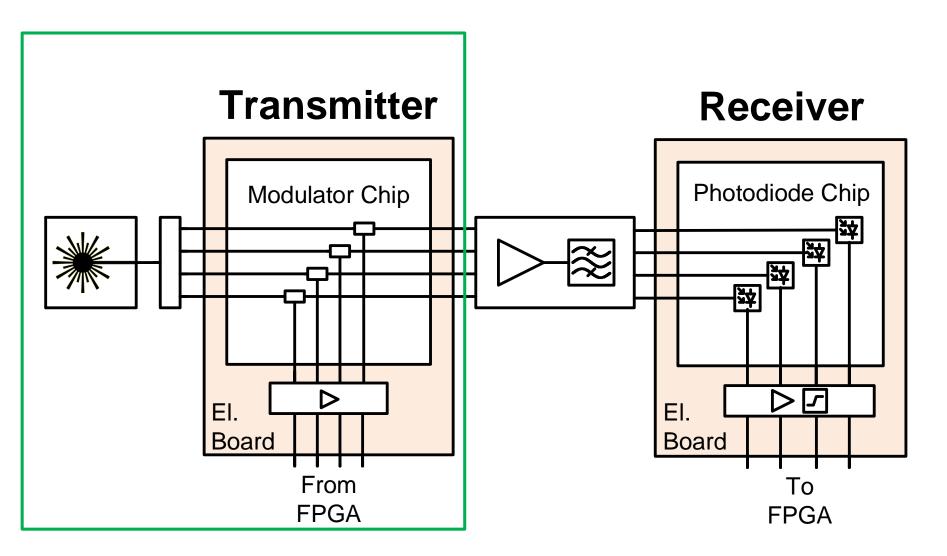

#### **Demonstrator**

# **Transmitter- PPM Chip (KIT)**

Phase Modulator:

- Optical

- Fed by external laser, split into four channels externally

- Pitch between channels: 50 µm and 35 µm

- Insertion loss (including GC): 30 dB

- Electrical

- Pad pitch: 100 µm (85 µm x 85 µm, GSG)

- Eletctrical probes or bonding for contacting

- No 50 Ω termination on chip

- Electrooptic

- VpiL: 1.1 Vmm (40 Gbit/s: 5 V<sub>pp</sub>),

- Bias or wavelength to determine operating point

## **Transmitter - FPGA**

What ST does:

- Send the rtl for the FPGA

- Choose discrete components for implementing the analog parts

- Act as consultant for the partner(s) who will design and manufacture the board

What ETH does:

- Provide an FPGA (ST cannot move their FPGA somewhere else)

- Design and manufacture the electronic board (laser driver, modulator driver, etc.) with the discrete components

- Provide electrical wire bonding or pico-probes

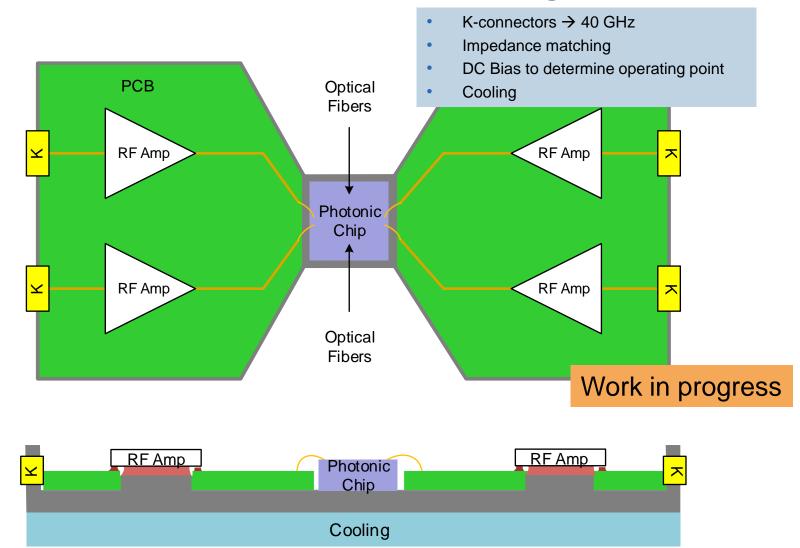

## **Transmitter – Packaging**

Main challenges

- Minimal light loss due to small pitch of 50 μm

- High frequencies require high precision alignment (K-connectors)

- High thermal density due to RF amplifiers

#### **Transmitter – Electrical Board and Housing**

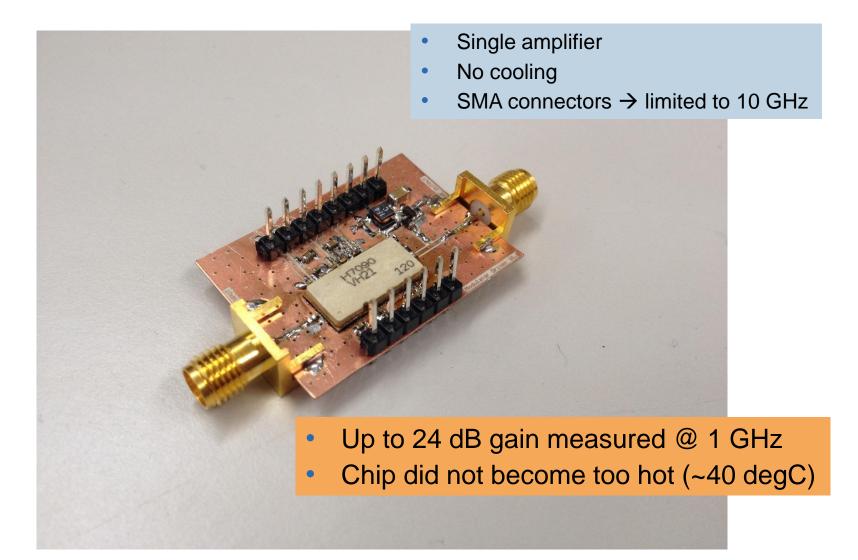

### **Transmitter – Prototype of Electrical Board**

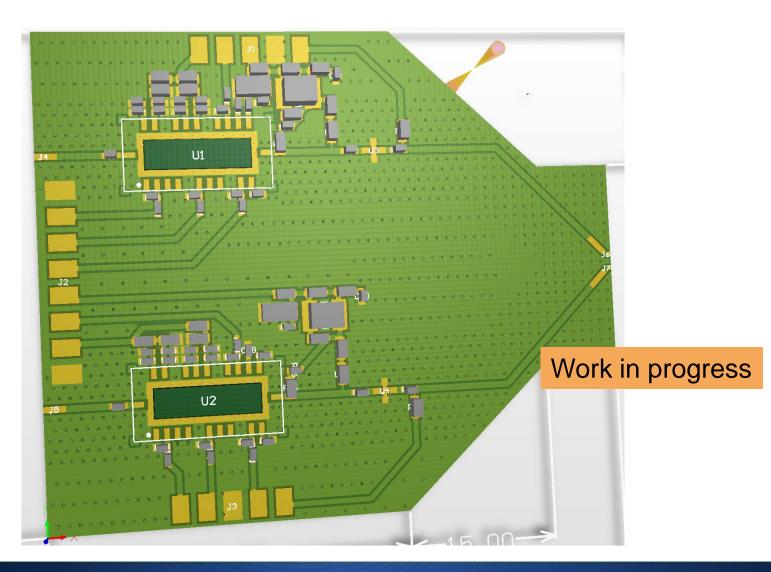

#### **Transmitter – Final Electrical Board**

#### **Optical Link**

#### **Multicore Fiber (Chiral Photonics)**

Main challenge: fiber array alignment accuracy

- 19 channels with 50 µm pitch

- Interchannel coupling <-35 dB (datasheet)</li>

- Allows for optical amplifier between transmitter and receiver

#### **Demonstrator**

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

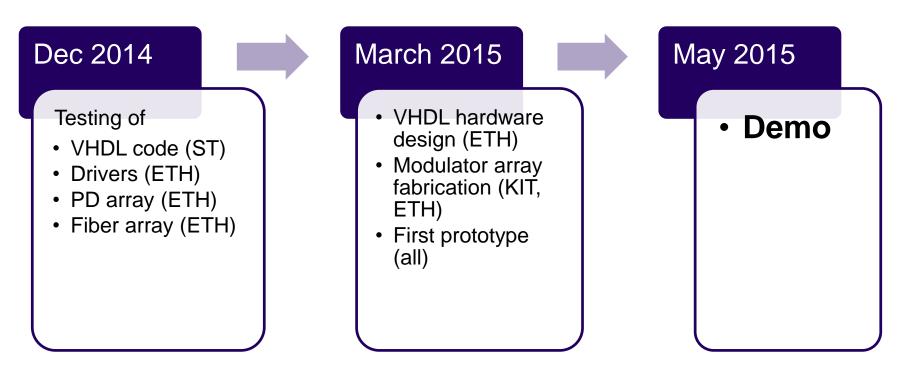

#### Timeline

VHDL code ST→ETH: 16.12.2014 ✓

Modulator drivers arrived at ETH: 08.12.2014 ✓

First prototype of board finished: 07.01.2015 ✓